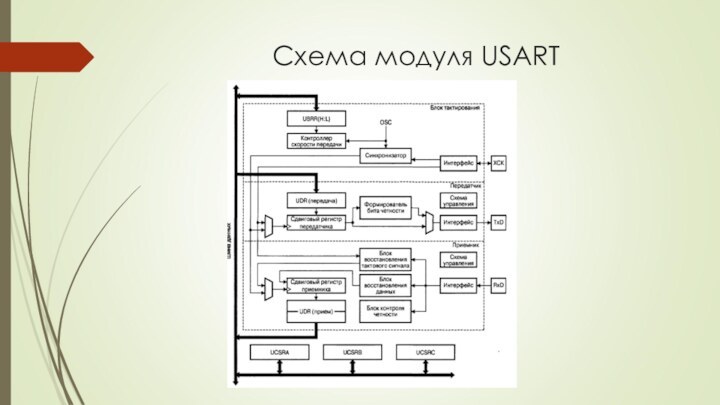

своем составе от одного до четырех модулей универсального синхронно/асинхронного

приемо-передатчика (USART).Все модули приемо-передатчиков обеспечивают полнодуплексный обмен по последовательному каналу, при этом скорость передачи данных может варьироваться в довольно широких пределах.