## Обмен с компьютером через СОМ порт в ATMEGA16

## Универсальный синхронный/асинхронный приемо-передатчик

- Все без исключения микроконтроллеры семейства Меда имеют в своем составе от одного до четырех модулей универсального синхронно/асинхронного приемо-передатчика (USART).

- Все модули приемо-передатчиков обеспечивают полнодуплексный об мен по последовательному каналу, при этом скорость передачи данных может варьироваться в довольно широких пределах.

## Модули USART в микроконтроллерах семейства Меда

| ATmega8515x/8535x | ATmega8x/16x/32x | ATmega64x/128x | ATmega48x/88x/168x | ATmega162x    | ATmega164x/324x/644x | ATmega165x,<br>ATmega325x/350x,<br>ATmega645x/6450x | ATmega640x/1280x/1281x | ATmega2560x/2561x                     |

|-------------------|------------------|----------------|--------------------|---------------|----------------------|-----------------------------------------------------|------------------------|---------------------------------------|

| •                 | •                | •              | • 1)               | •             | • 1)                 | •                                                   | • 1)                   | • 1)                                  |

|                   |                  | •              |                    | •             | • <sup>1)</sup>      |                                                     | • 1)                   | • 1)                                  |

|                   |                  |                |                    |               |                      |                                                     | • 1)                   |                                       |

|                   | - 355-           |                |                    | 571953000,000 |                      |                                                     | • 1)                   |                                       |

|                   |                  |                |                    |               |                      | • • • • • • • •                                     | • • • • • • • • •      | • • • • • • • • • • • • • • • • • • • |

## Модули USART в микроконтроллерах семейства Меда

Модули USART, реализованные в микроконтроллерах семейства, могут обнаруживать следующие внештатные ситуации:

□переполнение;

□ошибка кадрирования;

□неверный старт-бит.

#### Выводы, используемые модулями USART

| Назва-<br>ние | ATmega8515x    | ATmega8535x | ATmega8x | ATmega16x/32x | ATmega64x/128x | ATmega48x/88x/168x | ATmega162x | ATmega164x/324x/644x | ATmega165x,<br>ATmega325x/3250x,<br>ATmega645x/6450x | ATmega640x/1280x/2560x | ATmega1281x/2561x | Описание                                             |

|---------------|----------------|-------------|----------|---------------|----------------|--------------------|------------|----------------------|------------------------------------------------------|------------------------|-------------------|------------------------------------------------------|

| RXD           | PD0            | PD0         | PD0      | PD0           | _              | PD0                | _          | _                    | PE0                                                  | _                      | _                 | Вход USART0                                          |

| RXD0          | -              | _           | -        | _             | PE0            | _                  | PD0        | PD0                  | _                                                    | PE0                    | PE0               | DAOM COARTO                                          |

| TXD           | PDI            | PDI         | PDI      | PDI           | -              | PDI                | _          | -                    | PEI                                                  | _                      | _                 | Выход USART0                                         |

| TXD0          | 22-0           |             | _        | -             | PE1            | - N                | PDI        | PDI                  | _                                                    | PE1                    | PE1               | DBIXOL USAKTO                                        |

| XCK           | PD4            | PB0         | PD4      | PB0           | _              | PD4                | PD4        | _                    | PE2                                                  | _                      | _                 | Вход/выход вне-                                      |

| XCK0          | _              | _           | _        | -             | PE2            | -                  | _          | PB0                  | _                                                    | PE2                    | PE2               | шнего тактового<br>сигнала USART0                    |

| RXD1          | -              | -           | _        | _             | PD2            | -                  | PB2        | PD2                  | _                                                    | PD2                    | PD2               | Вход USART1                                          |

| TXD1          | ( <del>-</del> | -           | _        | -             | PD3            | -                  | PB3        | PD3                  | _                                                    | PD3                    | PD3               | Выход USART1                                         |

| XCK1          | _              | _           | _        | _             | PD5            | _                  | PD2        | PD4                  | -                                                    | PD5                    | PD5               | Вход/выход вне-<br>шнего тактового<br>сигнала USART1 |

| RXD2          | _              | _           | _        | _             | _              | _                  | _          | -                    |                                                      | PH0                    | _                 | Вход USART2                                          |

| TXD2          | -              | _           | _        | _             | -              | _                  | _          | _                    | _                                                    | PH1                    | _                 | Выход USART2                                         |

| XCK2          | -              | _           | _        | _             | _              | _                  | _          | _                    | _                                                    | PH2                    | _                 | Вход/выход вне-<br>шнего тактового<br>сигнала USART2 |

| RXD3          | _              | _           | _        | _             | _              | _                  | -          | _                    | _                                                    | PJ0                    | _                 | Вход USART3                                          |

| TXD3          | <u> </u>       | _           | -        | -             | _              | _                  | -          | -                    | -                                                    | PJ1                    | _                 | Выход USART3                                         |

| хск3          | _              | _           |          | _             | _              | _                  | _          | _                    | _                                                    | PJ2                    | -                 | Вход/выход вне-<br>шнего тактового<br>сигнала USART3 |

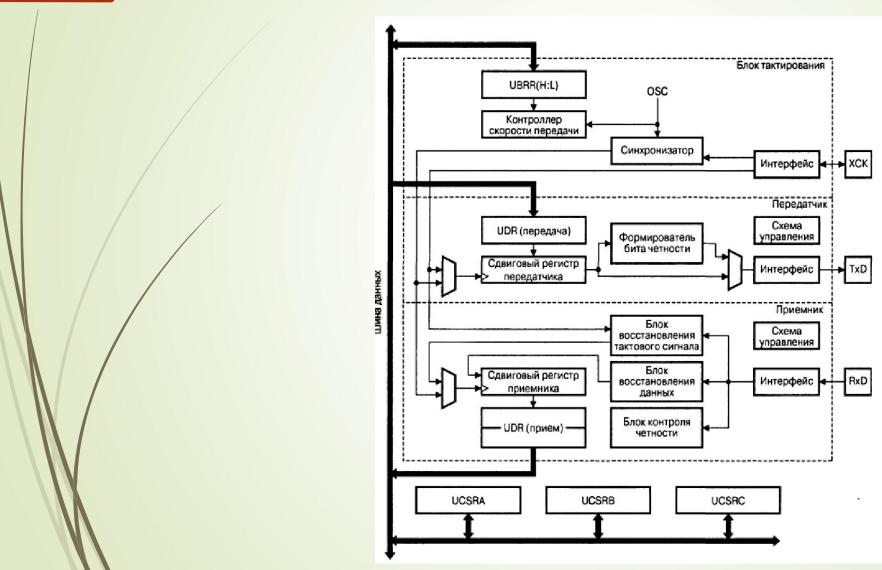

## Схема модуля USART

# Размещение регистров данных модулей USART

| Регистр | Адрес          | ATmega8515x/8535x | ATmega8x/16x/32x | ATmega64x/128x | ATmega48x/88x/168x | ATmega162x | ATmega164x/324x/644x | ATmega165x,<br>ATmega325x/3250x,<br>ATmega645x/6450x | ATmega640x/1280x/2560x | AFmega1281x/2561x | Описание                |

|---------|----------------|-------------------|------------------|----------------|--------------------|------------|----------------------|------------------------------------------------------|------------------------|-------------------|-------------------------|

| UDR     | \$0C<br>(\$2C) | •                 | •                |                |                    |            |                      |                                                      |                        |                   | Регистр данных<br>USART |

|         | (\$C6)         |                   |                  |                |                    |            |                      | •                                                    |                        |                   | OJAKI                   |

| UDR0    | \$0C<br>(\$2C) |                   |                  | •              |                    | •          |                      |                                                      |                        |                   | Регистр данных          |

|         | (\$C6)         |                   |                  |                | •                  |            | •                    |                                                      | •                      | •                 | USART0                  |

|         | \$03<br>(\$23) |                   |                  |                |                    | •          |                      |                                                      |                        |                   | Регистрданных           |

| UDRI    | (\$9C)         |                   |                  | •              |                    |            |                      |                                                      |                        |                   | USART1                  |

|         | (\$CE)         |                   |                  |                |                    |            | •                    |                                                      | •                      | •                 |                         |

| UDR2    | (\$D6)         |                   |                  |                |                    |            |                      |                                                      | •                      |                   | Регистрданных<br>USART2 |

| UDR3    | (\$136)        |                   |                  |                |                    |            |                      |                                                      | •                      |                   | Регистрданных USART3    |

# Регистры управления и состояния модулей USART

| Регистр | Апрес          | ATmega8515x/8535x | ATmega8x/16x/32x | ATmega64x/128x | ATmega48x/88x/168x | ATmega162x | ATmega164x/324x/644x | ATmega165x,<br>ATmega325x/3250x,<br>ATmega645x/6450x | ATmega640x/1280x/2560x | ATmega1281x/2561x | Описание                |

|---------|----------------|-------------------|------------------|----------------|--------------------|------------|----------------------|------------------------------------------------------|------------------------|-------------------|-------------------------|

| UCSRA   | \$0B<br>(\$2B) | •                 | •                |                |                    |            |                      |                                                      |                        |                   | Регистр<br>управления А |

| UCSRB   | \$0A<br>(\$2A) | •                 | •                |                |                    |            |                      |                                                      |                        |                   | Регистр<br>управления В |

| UCSRC   | \$20<br>(\$40) | •                 | •                |                |                    |            |                      |                                                      |                        |                   | Регистр<br>управления С |

| UCSR0A  | \$0B<br>(\$2B) |                   |                  | •              |                    | •          |                      |                                                      |                        |                   | Регистр А<br>управления |

|         | (\$C0)         |                   |                  |                | •                  |            | •                    | •                                                    | •                      | •                 | USART0                  |

| UCSR0B  | \$0A<br>(\$2A) |                   |                  | •              |                    | •          |                      |                                                      |                        |                   | Регистр В<br>управления |

|         | (\$C1)         |                   |                  |                | •                  |            | •                    | •                                                    | •                      | •                 | USART0                  |

|         | \$20<br>(\$40) |                   |                  |                |                    | •          |                      |                                                      |                        |                   | Регистр С               |

| UCSR0C  | (\$95)         |                   |                  | •              | 2.                 |            |                      |                                                      |                        |                   | управления<br>USART0    |

|         | (\$C2)         |                   |                  |                | •                  |            | •                    | •                                                    | •                      | •                 | Contro                  |

| UCSR1A  | \$02<br>(\$22) |                   |                  |                |                    | •          |                      |                                                      |                        |                   | Регистр А               |

|         | (\$9B)         |                   |                  | •              |                    |            |                      |                                                      |                        |                   | управления<br>USART1    |

|         | (\$C8)         |                   |                  |                |                    |            | •                    |                                                      | •                      | •                 |                         |

|         | \$01<br>(\$21) |                   |                  |                |                    | •          |                      |                                                      |                        |                   | Регистр В               |

| UCSRIB  | (\$9A)         |                   |                  | •              |                    |            |                      |                                                      |                        |                   | управления<br>USART1    |

|         | (\$C9)         |                   |                  |                |                    |            | •                    |                                                      | •                      | •                 |                         |

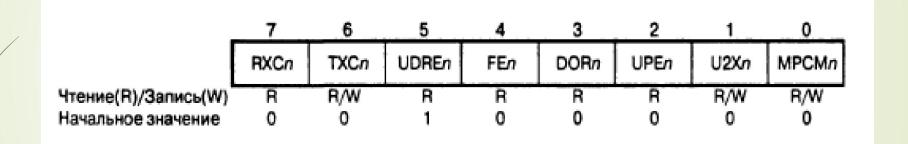

## Формат регистров UCSRA (UCSRnA)

## Биты регистров UCSRA (UCSRnA)

| Бит | Название        | Описание                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RXC<br>(RXCn)   | Флаг завершения приема. Флаг устанавливается в 1 при наличии непрочитанных данных в буфере приемника (регистр данных UDR). Сбрасывается флаг аппаратно после опустошения буфера. Если бит RXCIE (RXCIEn) регистра UCSRB (UCSRnB) установлен, то при установке флага генерируется запрос на прерывание «прием завершен»                                                                                                                                 |

| 6   | TXC<br>(TXCn)   | Флаг завершения передачи. Флаг устанавливается в 1 после передачи всех би тов посылки из сдвигового регистра передатчика при условии, что в регистр данных UDR не было загружено новое значение. Если бит TXCIE (TXCIEn) регистра UCSRB (UCSRnB) установлен, то при установке флага генерирует ся прерывание «передача завершена». Флаг сбрасывается аппаратно при вы полнении подпрограммы обработки прерывания или программно, записью в него лог. 1 |

| 5   | UDRE<br>(UDREn) | Флаг опустошения регистра данных. Данный флаг устанавливается в 1 при пустом буфере передатчика (после пересылки байта из регистра данных UDR в сдвиговый регистр передатчика). Установленный флаг означает, что в регистр данных можно загружать новое значение. Если бит UDRIE (UDRIEn) регистра UCSRB (UCSRnB) установлен, генерируется запрос на прерывание «регистр данных пуст». Флаг сбрасывается аппаратно, при записи в регистр данных        |

| 4   | FE<br>(FEn)     | Флаг ошибки кадрирования. Флаг устанавливается в 1 при обнаружении ошибки кадрирования, т. е. если первый стоп-бит принятой посылки равен 0. Флаг сбрасывается при приеме стоп-бита, равного 1                                                                                                                                                                                                                                                         |

| 3   | DOR<br>(DORn)   | Флаг переполнения. Флаг устанавливается в 1, если в момент обнаружения нового старт-бита в сдвиговом регистре приемника находится последнее принятое слово, а буфер приемника полон (содержит два байта). Флаг сбрасывается при пересылке принятых данных из сдвигового регистра приемни ка в буфер                                                                                                                                                    |

| 2   | UPE<br>(UPEn)   | Флаг ошибки контроля четности. Флаг устанавливается в 1, если в данных, находящихся в буфере приемника, выявлена ошибка контроля четности. При отключенном контроле четности этот бит постоянно сброшен в 0                                                                                                                                                                                                                                            |

| 1   | U2X<br>(U2Xn)   | Удвоение скорости обмена. Если этот бит установлен в 1, то коэффициент деления предделителя контроллера скорости передачи уменьшается с 16 до 8, удваивая тем самым скорость асинхронного обмена по последовательному каналу. Этот бит используется только при асинхронном режиме работы и в синхронном режиме должен быть сброшен                                                                                                                     |

| 0   | MPCM<br>(MPCMn) | Режим мультипроцессорного обмена. Если этот бит установлен в 1, ведомый микроконтроллер ожидает приема кадра, содержащего адрес. Калры, не содержащие адреса устройства, игнорируются                                                                                                                                                                                                                                                                  |

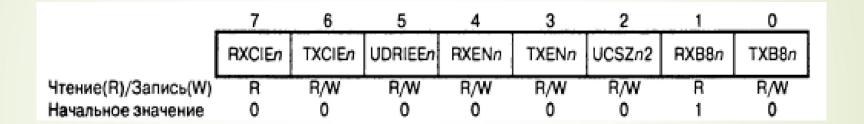

### Формат регистров UCSRB(UCSRnB)

## Биты регистров UCSRB (UCSRnB)

| Бит | Название          | Описание                                                                                                                                                                                                                                                                                                                      |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RXCIE<br>(RXCIEn) | Разрешение прерывания по завершении приема. Если данный бит установлен в 1, то при установке флага RXC (RXCn) регистра UCSRA (UCSRnA) генерируется прерывание «прием завершен» (если флаг I регистра SREG установлен в 1)                                                                                                     |

| 6   | TXCIE<br>(TXCIEn) | Разрешение прерывания по завершении передачи. Если данный бит установлен в 1, то при установке флага ТХС (ТХСп) регистра UCSRA (UCSRnA) генерируется прерывание «передача завершена» (если флаг I регистра SREG установлен в I)                                                                                               |

| 5   | UDRIE<br>(UDRIEn) | Разрешение прерывания при очистке регистра данных UART. Если данный бит установлен в 1, то при установке флага UDRE (UDREn) регистра UCSRA (UCSRnA) генерируется прерывание «регистр данных пуст» (если флаг I регистра SREG установлен в 1)                                                                                  |

| 4   | RXEN<br>(RXENn)   | Разрешение приема. При установке этого бита в 1 разрешается работа приемника USART и переопределяется функционирование вывода RXD (RXDn). При сбросе бита RXEN (RXENn) работа приемника запрещается, а его буфер сбрасывается. Значения флагов TXC(TXCn), DOR (DORn) и FE (FEn) при этом становятся недействительными         |

| 3   | TXEN<br>(TXENn)   | Разрешение передачи. При установке этого бита в 1 разрешается работа передатчика UART и переопределяется функционирование вывода TXD (TXDn). Если бит сбрасывается в 0 во время передачи, то выключение передатчика произойдет только после завершения передачи данных, находящихся в сдвиговом регистре и буфере передатчика |

| 2   | UCSZ2<br>(UCSZn2) | Формат посылок. Этот бит совместно с битами UCSZ1:0 (UCSZn1:0) регистра UCSRC (UCSRnC) используется для задания размера слов данных, передава емых по последовательному каналу                                                                                                                                                |

| 1   | RXB8<br>(RXB8n)   | 8-й бит принимаемых данных. При использовании 9-битных слов данных это бит содержит значение старшего бита принятого слова. Содержимое этого бита должно быть считано до прочтения регистра данных UDR                                                                                                                        |

| 0   | TXB8<br>(TXB8n)   | 8-й бит передаваемых данных. При использовании 9-битных слов данных содержимое этого бита является старшим битом передаваемого слова. Требуемое значение должно быть занесено в этот бит до загрузки байта данных в регистр UDR                                                                                               |

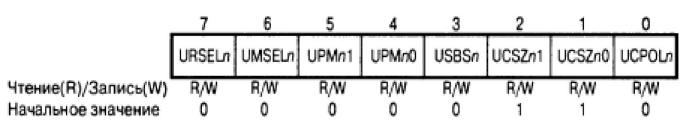

## Формат регистров UCSRC(UCSRnC)

ATmega8515x/8535x

ATmega8x/16x/32x

ATmega162x

ATmega165x/325x/3250x

ATmega645x/6450x

## Биты регистров UCSRC (UCSRnC)

| Бит | Название                        | Описание                                                                                                                                                                                                                                                                        |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | UMSELn1                         | Режим работы USART (модели 48x/88x/168x, 164x/324x/644x и 640x/1280x/1281x/2560x/2561x). Совместно с битом UMSELn0 определяет режим работы модуля USART                                                                                                                         |

| 7   | URSEL <sup>1)</sup><br>(URSELn) | Выбор регистра. Этот бит определяет, в какой из регистров модуля производится запись. Если бит установлен в 1, обращение производится к регистру UCSRC (UCSRnC). Если же бит сброшен в 0, обращение производится к регистру UBRRH (UBRRnH). Подробнее — см. следующий подраздел |

| 6   | UMSEL<br>(UMSELn)               | Режим работы USART. Если бит сброшен в 0, то модуль работает в асинхронном режиме. Если бит установлен в 1, то модуль работает в синхронном режиме                                                                                                                              |

| 0   | UMSELn0                         | Режим работы USART (модели 48x/88x/168x, 164x/324x/644x и 640x/1280x/1281x/2560x/2561x). Совместно с битом UMSELn1 определяет режим работы модуля USART                                                                                                                         |

| 5   | UPM1<br>(UPMn1)                 | Режим работы схемы контроля и формирования бита четности. Эти биты опре-                                                                                                                                                                                                        |

| 4   | UPM0<br>(UPMn0)                 | деляют функционирование схем контроля и формирования бита четности (см. подраздел 13.2.2)                                                                                                                                                                                       |

| 3   | USBS<br>(USBSn)                 | Количество стоп-битов. Этот бит определяет количество стоп-битов, посылаемых передатчиком. Если бит сброшен в 0, передатчик посылает 1 стоп-бит, если установлен в 1, то 2 стоп-бита. Для приемника содержимое этого бита безразлично                                           |

| 2   | UCSZ1<br>(UCSZn1)               | Формат посылок. Совместно с битом UCSZ2 (UCSZn2) регистра UCSRB (UCSRnB) эти биты определяют количество битов данных в посылках                                                                                                                                                 |

| 1   | UCSZ0<br>(UCSZn0)               | (размер слова)                                                                                                                                                                                                                                                                  |

## Биты регистров UCSRC (UCSRnC)

| Бит | Название                                    | Описание                            |                                                                                                                                                                                                                    |                                          |  |  |  |  |

|-----|---------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|

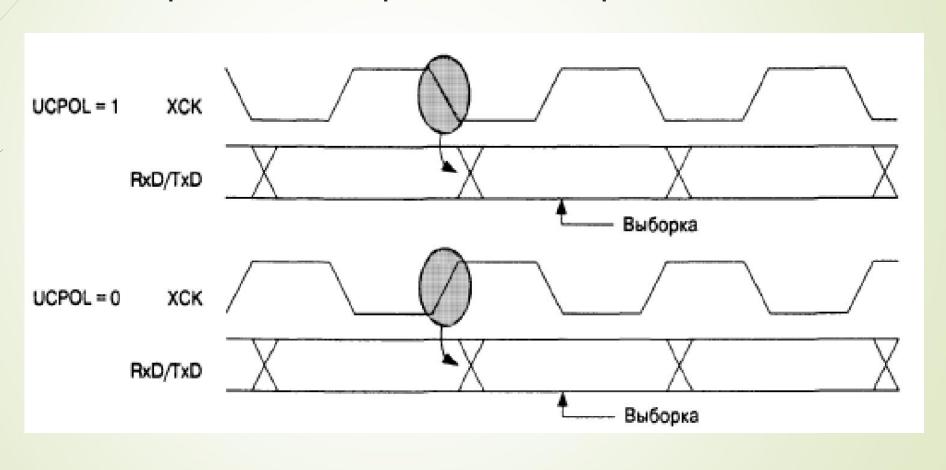

|     |                                             | дачи и считыван<br>работе в синхрог | Полярность тактового сигнала. Значение этого бита определяет мометачи и считывания данных на выводах модуля. Бит используется толо работе в синхронном режиме. При работе в асинхронном режиме онбыть сброшен в 0. |                                          |  |  |  |  |

| 0   | UCPOL<br>(UCPOLn)                           | UCPOL<br>(UCPOLn)                   | Выдача данных на вывод<br>TXD (TXDn)                                                                                                                                                                               | Считывание данных с вывода<br>RXD (RXDn) |  |  |  |  |

|     |                                             | 0                                   | Спадающий фронт ХСК (ХСКn)                                                                                                                                                                                         | Нарастающий фронт ХСК (ХСКn)             |  |  |  |  |

|     |                                             | 1                                   | Нарастающий фронт ХСК (ХСКn)                                                                                                                                                                                       | Спадающий фронт ХСК<br>(ХСК <i>n</i> )   |  |  |  |  |

| 1)  | 1) Зарезервирован в моделях ATmega64x/128x. |                                     |                                                                                                                                                                                                                    |                                          |  |  |  |  |

### Скорость приема/передачи

В асинхронном режиме, а также в синхронном режиме при работе в качестве ведущего скорость приема и передачи данных задается контроллером скорости передачи, работающим как делитель системного тактового сигнала с программируемым коэффициентом деления. Коэффициент определяется содержимым регистра контроллера UBRR (UBRRn)

### Скорость приема/передачи

- □ Скорость обмена определяется следующим образом:

- асинхронный режим (обычный, U2Xn = 0)

$$BAUD = \frac{f_{CK}}{16 \cdot (UBRR + 1)}$$

• асинхронный режим (ускоренный, U2Xn = 1)

$$BAUD = \frac{f_{CK}}{8 \cdot (UBRR + 1)}$$

• синхронный режим ведущего

$$BAUD = \frac{f_{CK}}{2 \cdot (UBRR + 1)},$$

## Размещение регистров контроллера скорости передачи

| Модель                           | Регистры      | Адрес                   |

|----------------------------------|---------------|-------------------------|

| ATmega8515x/8535x 1)             | UBRRH:UBRRL   | \$20 (\$40):\$09 (\$29) |

| ATmega8x/16x/32x 1)              | UBRRH:UBRRL   | \$20 (\$40):\$09 (\$29) |

| AT(4-/120                        | UBRR0H:UBRR0L | (\$90):\$09 (\$29)      |

| ATmega64x/128x                   | UBRR1H:UBRR1L | (\$98):(\$99)           |

| ATmega48x/88x/168x               | UBRR0H:UBRR0L | (\$C5):(\$C4)           |

| ATmega162x 1)                    | UBRR0H:UBRR0L | \$20 (\$40):\$09 (\$29) |

| Almega 162x 5                    | UBRR1H:UBRR1L | \$3C (\$5C):\$00 (\$20) |

| ATmoon 16 do: /20 do: /6 dd:     | UBRR0H:UBRR0L | (\$C5):(\$C4)           |

| ATmega164x/324x/644x             | UBRR1H:UBRR1L | (\$CD):(\$CC)           |

| ATmega165x/325x/3250x/645x/6450x | UBRR0H:UBRR0L | (\$C5):(\$C4)           |

|                                  | UBRR0H:UBRR0L | (\$C5):(\$C4)           |

| AT                               | UBRR1H:UBRR1L | (\$CD):(\$CC)           |

| ATmega640x/1280x/2560x           | UBRR2H:UBRR2L | (\$D5):(\$D4)           |

|                                  | UBRR3H:UBRR3L | (\$135):(\$134)         |

| ATman 1201v /2561v               | UBRR0H:UBRR0L | (\$C5):(\$C4)           |

| ATmega1281x/2561x                | UBRR1H:UBRR1L | (\$CD):(\$CC)           |

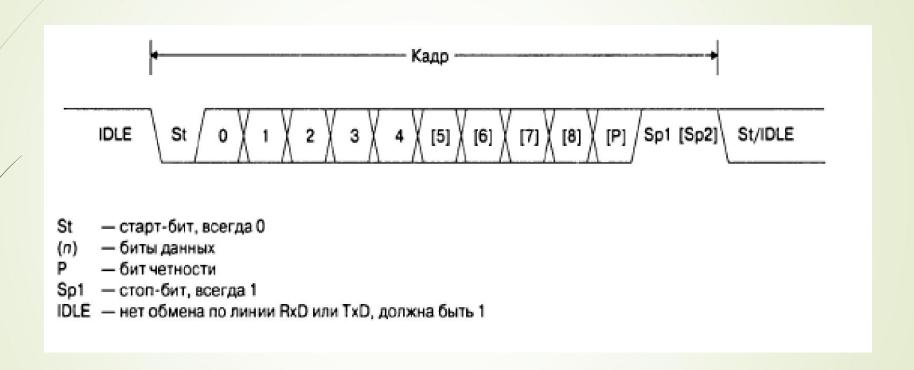

- □ Под кадром в данном случае понимается совокупность одного слова данных и сопутствующей информации

- Кадр начинается со старт-бита, за которым следует младший бит слова данных

- После старшего бита слова данных следует один или два стоп-бита

- Если включена схема формирования бита четности, он включается между старшим битом слова данных и первым стоп-битом.

Формат кадра определяется различными битами регистров UCSRB(UCSRnB) и UCSRC (UCSRnC). В частности, размер слова данных определяется битами UCSZ2...UCSZ0 (UCSZn2...UCSZnO) В соответствии с данной таблицей:

| UCSZ2<br>(UCSZn2) | UCSZ1<br>(UCSZn1) | UCSZ0<br>(UCSZn0) | Размер слова данных |

|-------------------|-------------------|-------------------|---------------------|

| 0                 | 0                 | 0                 | 5 бит               |

| 0                 | 0                 | 1                 | 6 бит               |

| 0                 | 1                 | 0                 | 7 бит               |

| 0                 | 1                 | 1                 | 8 бит               |

| 1                 | 0                 | 0                 | Зарезервировано     |

| 1                 | 0                 | 1                 | Зарезервировано     |

| 1                 | 1                 | 0                 | Зарезервировано     |

| 1                 | 1                 | 1                 | 9 бит               |

Биты UPM1:UPM0 (UPIVM:UPMAJO) регистра UCSRC (UCSRA/C) определяют функционирование схемы контроля четности модулей USART согласно таблице:

| UPM1 (UPMn1) | UPM0 (UPMn0) | Режим работы схемы                            |

|--------------|--------------|-----------------------------------------------|

| 0            | 0            | Выключена                                     |

| 0            | 1            | Зарезервировано                               |

| 1            | 0            | Включена, проверка на четность (even parity)  |

| 1            | 1            | Включена, проверка на нечетность (odd parity) |

#### Передача данных

□ Работа передатчика разрешается установкой в 1 бита TXEN (TXENn) регистра UCSRB (UCSRAn). При установке бита вывод TXD (TXDn) подключается к передатчику USART и начинает функционировать как выход независимо от установок регистров управления портом. Если используется синхронный режим работы, то переопределяется также функционирование вывода XCK (XCKn).

## Временные диаграммы для синхронного режима работы USART

#### Прием данных

□ Работа приемника разрешается установкой бита RXEN (RXENn) ре гистра UCSRB (UCSRnB). При установке бита вывод RXD (RXDn) под ключается к приемнику USART и начинает функционировать как вход независимо от установок регистров управления портом. Если используется синхронный режим работы, переопределяется также функционирование вывода XCK (XCKn).