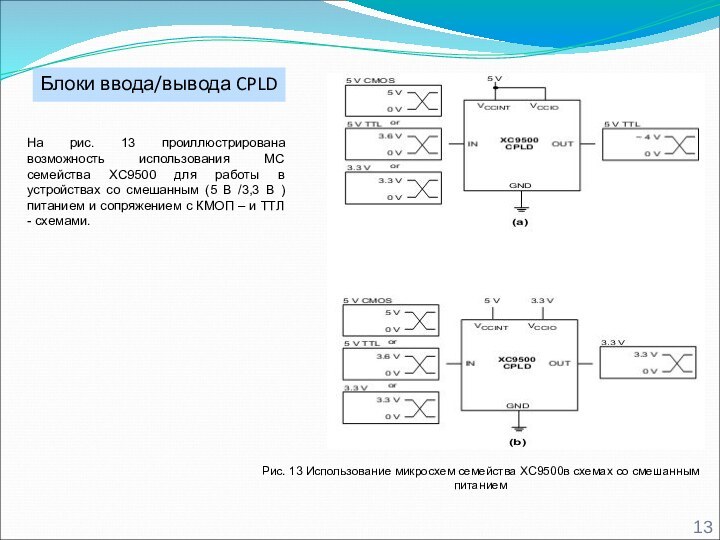

CPLD является серия XC9500 и ее разновидности XC9500, XC9500XL

и XC9500XV с напряжением питания ядра 5, 3.3 и 2.5В соответственно. Параметрами ПЛИС является количество макроячеек, количество триггеров и количество эквивалентных логических вентилей. Общей характеристикой ПЛИС XC9500/XL/XV является то, что устройства с меньшим напряжением питания обладают более высоким быстродействием и большей функциональностью распределителей термов.

Другим семейством ПЛИС CPLD является семейство CoolRunner. Это семейство отличается пониженным энергопотреблением (статический ток не превышает 100 мкА). Функциональные возможности и порядок проектирования в целом подобны ПЛИС серии XC9500. Однако технические решения имеют существенные отличия. Прежде всего функциональные блоки ПЛИС CoolRunner содержат матрицу ПЛМ в отличие от ПМЛ-матрицы в XC9500, что позволяет оптимизировать использование ресурсов кристалла при реализации сложных проектов. Однако данное отличие прозрачно для разработчика и не делает необходимым его специальный учет при проектировании цифровых устройств.

В семейство CoolRunner входят серия XPLA3 с напряжением питания ядра 3,3 В и семейство CoolRunner-II с напряжением питания ядра 1,8 В. Отличием семейства CoolRunner-II является поддержка большого числа электрических стандартов ввода/вывода.

Устройства CPLD относятся к устройствам начального уровня и предназначены для реализации устройств небольшого логического объема.

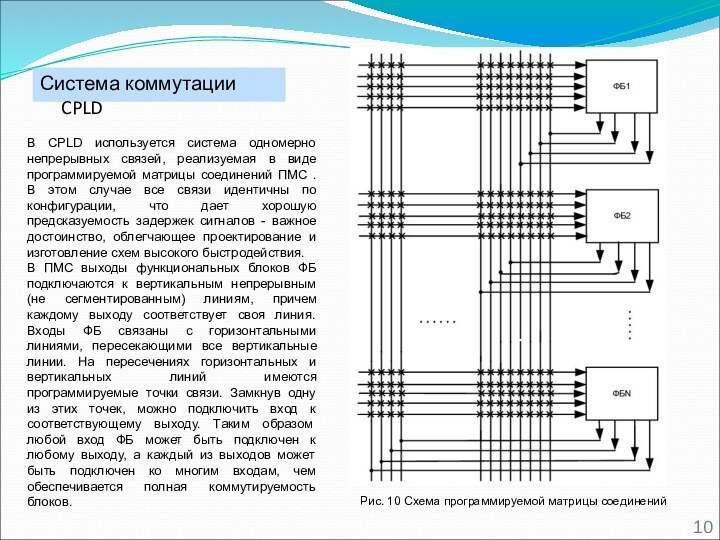

Достоинства: простота структуры и большое количество трассировочных ресурсов дает свободу в размещении проекта на кристалле; хорошая предсказуемость временных характеристик.

Недостатки: CPLD мало пригодны для проектирования устройств, насыщенных триггерами.