Слайд 2

ЗАГАЛЬНА ХАРАКТЕРИСТИК

Позиціонуються як процесори початкового і середнього рівня

ціни і потужності. В новому модельному ряду замінили морально

застарілі Core 2 Duo на архітектурі Intel Core

Мають вбудований графічний процесор і вбудований контролер пам’яті. Процесори,

Слайд 3

INTEL CORE I3

Сімейство процесорів x86-64 від Intel, спрощена версія Intel Core i5.

Всі існуючі моделі процесорів — двоядерні. Назва Core i3 нічого не

означає, вона лиш продовжує серію брендів Core 2 і Core.[1] Офіційно процесори цього сімейства оголошені у продаж з 7 січня 2010 року

Слайд 4

INTEL CELERON

Велике сімейство бюджетних x86-сумісних процесорів компанії Intel. Сімейство Celeron призначалося для

побудови дешевих комп'ютерів. Процесори Celeron спочатку позиціонувалися як процесори

нижнього сегменту, і призначалися для розширення частки ринку компанії Intel. Однією з причин

Слайд 5

МАЮТЬ ВБУДОВАНИЙ ГРАФІЧНИЙ ПРОЦЕСОР І ВБУДОВАНИЙ КОНТРОЛЕР ПАМ’ЯТІ. ПРОЦЕСОРИ CORE

I3 З’ЄДНУЮТЬСЯ ІЗ ЧІПСЕТОМ ЧЕРЕЗ ШИНУ DMI АБО DMI 2.0. ПІДТРИМУЮТЬ

ІНСТРУКЦІЇ — MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2. ПІДТРИМУЮТЬ ТЕХНОЛОГІЇ — ENHANCED INTEL SPEEDSTEP TECHNOLOGY (EIST), INTEL 64, XD BIT (AN NX BIT IMPLEMENTATION), INTEL VT-X, SMART-CACHE, А ТАКОЖ ТЕХНОЛОГІЮ HYPER-THREADING, ЧЕРЕЗ ЩО ОПЕРАЦІЙНА СИСТЕМА РОЗПІЗНАЄ ДАНИЙ ДВОХПРОЦЕСОРНИЙ ПРОЦЕСОР, ЯК ЧОТИРИПРОЦЕСОРНИЙ.

Слайд 6

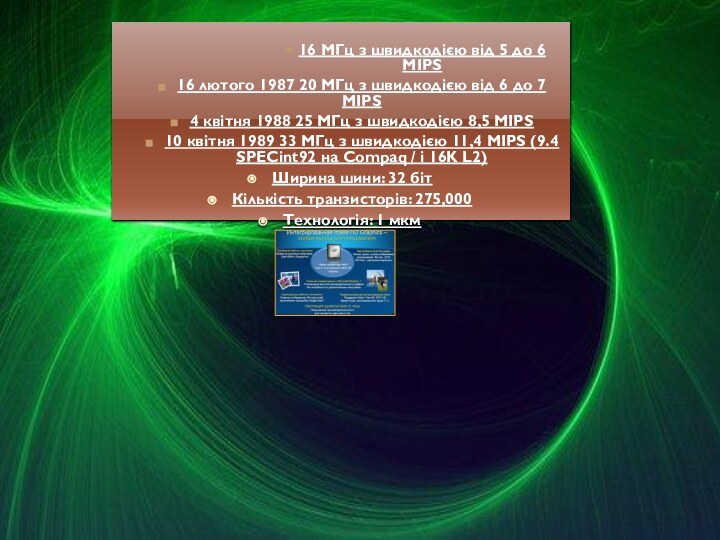

16 МГц з швидкодією від 5 до 6

MIPS

16 лютого 1987 20 МГц з швидкодією від 6

до 7 MIPS

4 квітня 1988 25 МГц з швидкодією 8,5 MIPS

10 квітня 1989 33 МГц з швидкодією 11,4 MIPS (9.4 SPECint92 на Compaq / i 16K L2)

Ширина шини: 32 біт

Кількість транзисторів: 275,000

Технологія: 1 мкм

Слайд 7

COVINGTON

Перші процесори сімейства Celeron були випущені на ядрі Covington, що

являє собою ядро Deschutes без кеша L2. Відсутність кеша L2 призвело до

того, що процесор був помітно менш продуктивним, ніж навіть Pentium MMX, і це при тому, що частота Celeron була більше. У результаті вийшло так, що на зміну старому процесору прийшов процесор з новою архітектурою, але при цьому помітно повільніший. Більшість експертів негативно відгукувалися про новий

Слайд 8

MENDOCINO

ntel знала про поганої репутації перших Celeron і

тому не стала повторювати помилки та випустила нове ядро

з кешем L2. Ядро Mendocino багато в чому має ту ж архітектуру, що і Katmai, хоча і випущено раніше. Кеш L2 був інтегрований в ядро і, відповідно, розміщувався на одному з ним кристалі, що дозволило працювати кешу L2 на частоті ядра. Тому, хоча частота FSB була навмисно

Слайд 9

КЛАСИФІКАЦІЯ МІКРОПРОЦЕСОРІВ

Для опису МП як функціональних пристроїв необхідно

охарактеризувати формат команд і даних, що обробляються, кількість, тип

і гнучкість команд, методи адресації даних, число внутрішніх регістрів загального призначення і регістрів результату, можливості

Слайд 10

32-бітові процесори: мікроархітектура P6/Pentium M[ред. • ред. код]

Pentium Pro[ред. • ред. код]

Мікропроцесор

для серверів і робочих станцій з підтримкою симетричної багатопроцесорності

(SMP)

Представлений: 1 листопада 1995

Попередник Pentium II і III

Використовувався переважно в

![Сучасні процесори INTEL 32-бітові процесори: мікроархітектура P6/Pentium M[ред. • ред. код]Pentium Pro[ред. • ред. код]Мікропроцесор для серверів і робочих](/img/tmb/15/1448791/99d95c3ac04ea11df4c0233269f1ae7e-720x.jpg)